Hello man, here some pros and cons

Analog IQ demo

- less power consumption in the DSP/FPGA because lower clk

- less expensive ADCs but need two of them

- will have more IQ imbalance

- for low SNR or high eye performance will need digital IQ crosstalk/imbalance correction algorithm

- will need two antialiasing low pass filters (that will increase IQ imbalance)

Digital IQ

- perfect mathematical assumption of demodulation (perfect mixer multiplication, "no" mixer harmonics, higher TOI)

- will need higher clk FPGA and ADC

- needs high dynamic range ADC

- IQ lowpass filters after mixer will be digital FIR filters (a lot of multiplication or DSP slices needed)

- will need one steep low pass anti aliasing filter at ADC input

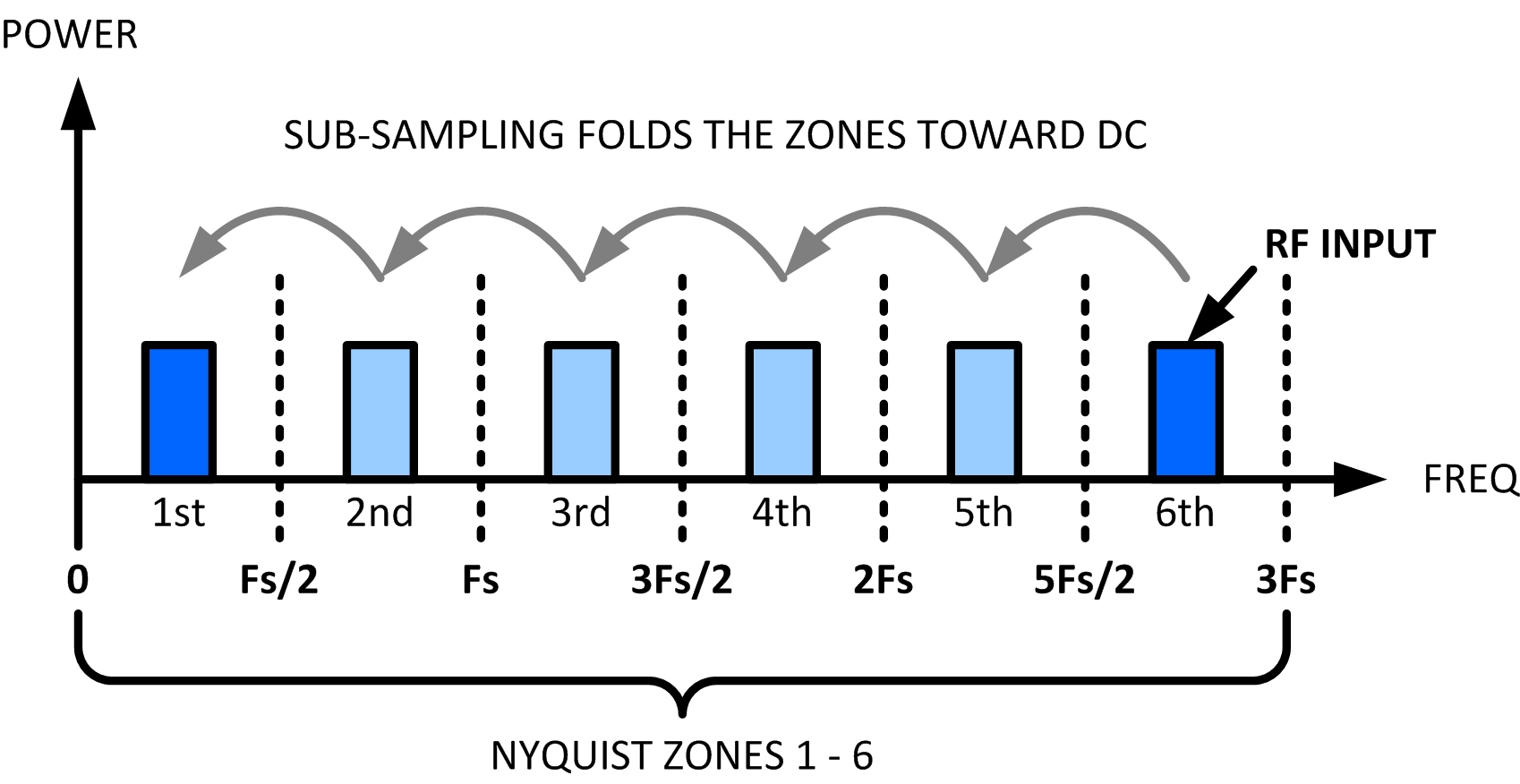

In the digital IQ you can use nyquist subsampling / sampling down conversion to reduce the sampling rate needed.

If your signal is centered at 30MHz and have a 10MHz bandwidth, you actually need only a 20MegSample ADC.

The ADC needs to have 30MHz of analog bandwidth, but the sampling rate needs to be only double the bandwidth of the signal.

Sampling will down covert the signal for you (as sampling is very similar to mixing), in this case the aliasing will be your friend!