If your FPGA is generating separate Y and C signals, I don't see the problem.

You'll need to tell us a bit more. And no GitLab/GitHub, please, I've had it with those. Nerdy as nerdy can get.

Signal plots etc.

Hi Benta,

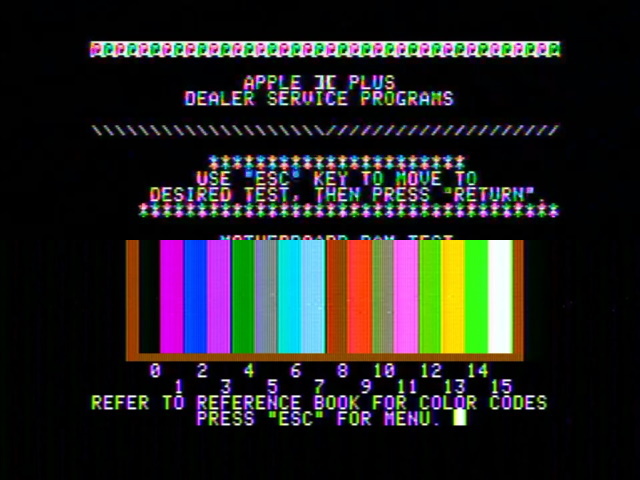

Just for clarity, the issue is only through composite video when combining the Y / C signals to make composite where the issue (caused by the luma signal) can be seen clearly in this image. The change between pixels in the luma signal is being interpreted by the TV as color and needs to be filtered.

I am generating the signals separately, but due to the resource intensiveness of filters in the FPGA, I want to notch out any frequency in near the 3.579 Mhz region of the luma signal. The current design works to get ride of 90% of the problem but attenuating the filter to get that extra 10% is causing me a lot of issues. Largely the following:

- If using a shunt filter, when i combine the two signals, I start to filter out the chroma signal as well which kills the color signals because it modulates color at 3.579 Mhz.

- If I try developing a second order notch filter starting with a shunt filter through a series filter, I can attenuate the signal a bit better but it causes a delay between the luma and chroma signals and I get ghosting on the screen.

- I'm not sure how to model 2 sources in LTspice to help me with the development process.

Oddly enough, in my circuit, keeping a 6.8uH inductor (5% tol), I get no major changes in how much rainbowing I can address, and Ive found 300pF to be the sweet spot.

- I can not add resistance to the luma signal because the 75ohm load of the TV just acts as a voltage divider.

I dont know how many passive options I have here but I wanted to see if I could address it with passive LC components, and I've considered adding an active buffer before both signals but I really need to find a proper way to simulate it before I go out and start building a prototype.

I've include a snap shot of my current design, and for a series filter it works well enough where it does not reduce the sharpness too much but the attenuate needs to be stronger ... I think?

Because of the design of the DAC the following are assumed.

- Input voltage is 3.2V for the luma signal where the input resistance of the filter is 264 ohms. (Output voltage is 720mV, with a 75Ohm Load)

- Input voltage is 1.8V for the chroma signal where the input resistance of the chroma signal is 126 ohms (Output voltage is 700mV, with a 75Ohm Load)

-fpga-ntscpal-encoder/?action=dlattach;attach=1494337)

I've been causing me a lot of headaches to get the last 5-10% =/

Maybe to add a bit more as well here is what the three signals should look like using a standard SMPTE image:

Luma(This can have very large changes depending on the brightness changes pixel to pixel on the screen):

Chroma:

Composite: