Someone may find this amusing.

I have a 32F417VGT6 project. The RAM goes 0x20000000 to 0x2001ffff. 1MB FLASH. A couple of boards were built with a 32F437VGT7 which is almost 100% identical but has an extra 64k RAM, so that goes 0x20000000 to 0x2002ffff.

Actually I think the 32F437VGT7 has 2MB FLASH while a 32F437VGT6 would be 1MB but it is very hard to establish the part numbers (nothing in the data sheet).It was not realised two of the boards were the 437 and indeed they run the same. In fact, speaking to one expert, the only known other difference in terms of backwards compatibility at the binary level is something around the way Vbat is measured with one of the internal ADCs.

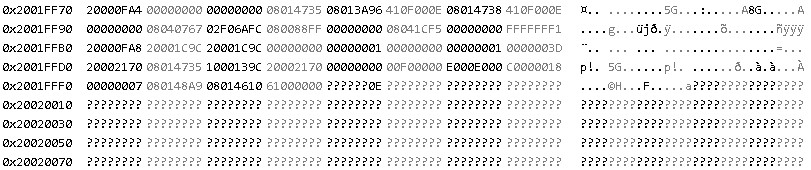

But Cube does some funny stuff. With the 417, viewing memory (target stopped, obviously) around the top of RAM shows this

which is correct; the real physical end of memory is 0x2001ffff.

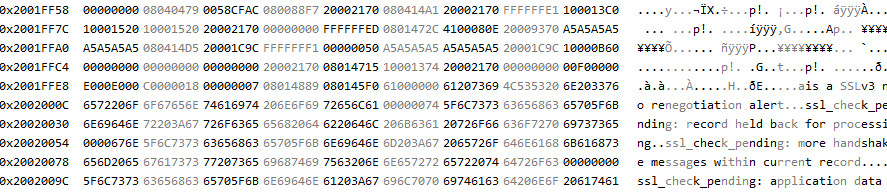

I have an 8k stack at the top of memory, hence the values seen below 0x20020000. But on the 437, whose RAM continues past this, I see this data after 0x2001ffff

and I have no idea where this comes from. A watchpoint in there is never triggered, and no code of mine should be using that extra 64k. I recognise the data; it also appears lower down (it is stuff from MbedTLS) so this is a kind of mirroring thing. If I edit some of those values (say at 0x20020050) to say 0 and restart the system, they stay at zero until the very last instruction of the startupxxxx.s file and then as soon as I step (asm instruction step mode) into main.c those locations change to the values shown above. No interrupts, DMA, etc is running at this point.

I reckon Cube is just imagining data there because the CPU ID which it gets via the debugger is not the CPU type which has been configured in it.

It is possible for data in that memory to persist for ages since nothing is accessing it, but equally nothing should be writing in there.