1. The RP2040 board footprint has too small holes (0.5mm), if these are the typical 100 mil headers with square pins then 1mm hole is normal.

2. On your TFT connector the spacing seems rather tight, check if that is within your pcb fab specs.

3. Where you route the relay signal lines (same applies to relay power lines) they are very close together, since you have the space you could route them a bit further apart to not push manufacturer specs and reduce parasitic capacitance between them. Here is a quick and dirty example:

4. While we're at the driver IC it's best to place a capacitor across the power lines to reduce the effects of our long power trace having inductance (also you can route the power on top side without breaking the ground plane).

5. At the buck IC you got a missing connection, learn to use the design rule checker, it saves you from mistakes like this.

6. As for the routing of the buck, read the recommended layout section of the datasheet.

In general when routing such things we place the power components like inductor first, and try to keep the loop area small. Remember that all traces have inductance proportional to their length. Due to that, routing the gnd of the chip and capacitors to resistor leg with long traces instead of using separate vias for every one of them that would connect them to low inductance ground plane is bad. A quick example of how i might route the buck:

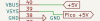

7. Something i didn't understand on the schematic is the rp2040 board VBUS VSYS pins and it seems the VBUS pin is the one that power is provided to.

But the datasheet says:

"VBUS is the micro-USB input voltage, connected to micro-USB port pin 1. This is nominally 5V (or 0V if the USB is not connected or not powered). VSYS is the main system input voltage, which can vary in the allowed range 1.8V to 5.5V, and is used by the on-board SMPS to generate the 3.3V for the RP2040 and its GPIO"

So i think it would be better to power VSYS so that in case USB is plugged in while board is powered there is no power conflict.