The MH74S287 is a PROM built by Tesla with a memory depth of 1024Bit. It is a bipolar Schottky PROM with tristate outputs.

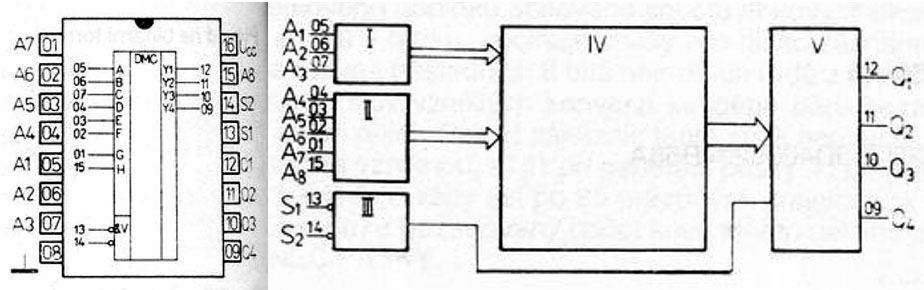

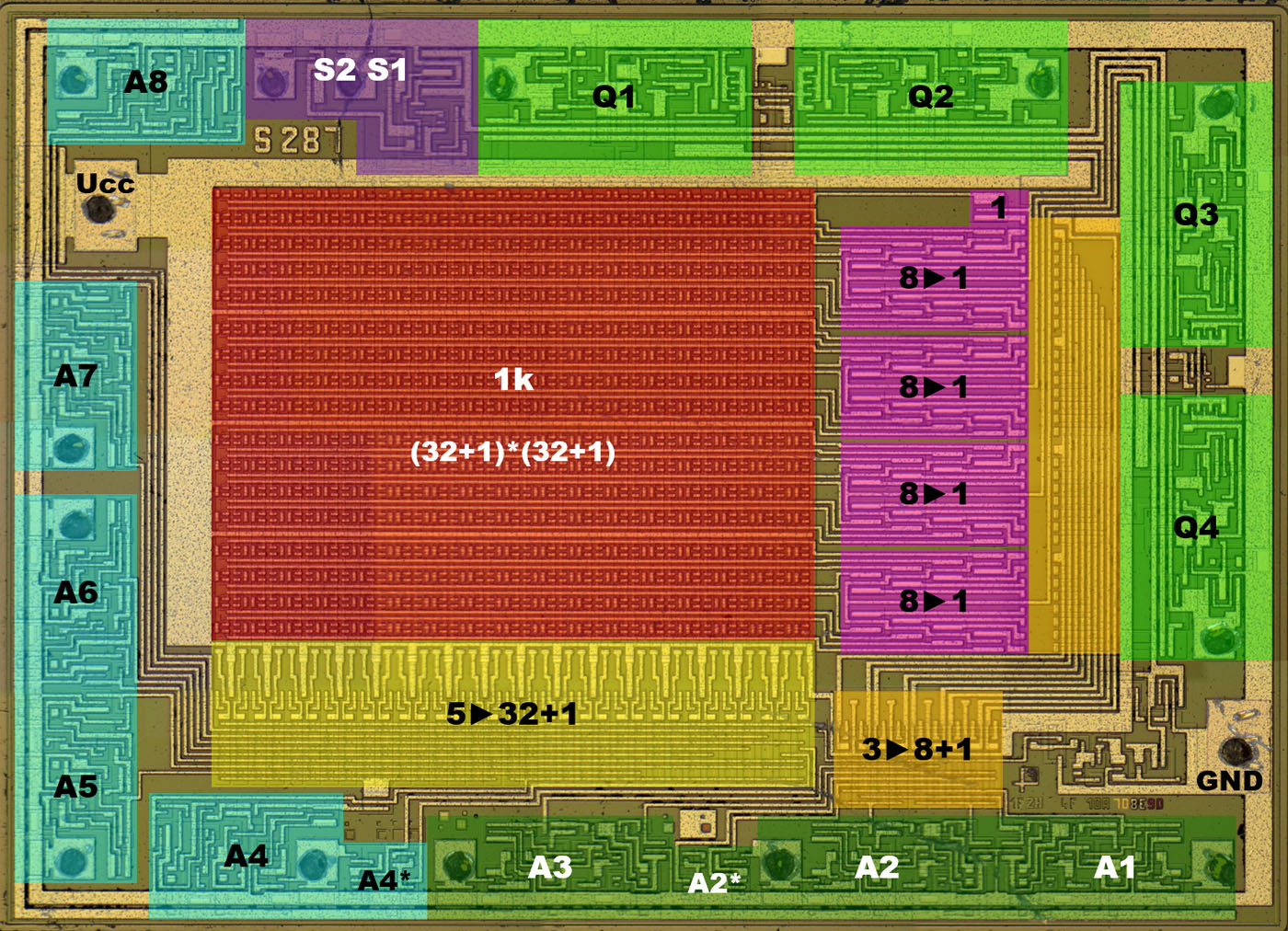

The datasheet shows the basic structure of the MH74S287. The memory (IV) contains 32x32 memory cells. The first address decoder (I) generates eight control signals from the first three address lines, which activate one line each from four memory groups. The second address decoder (II) generates 32 control signals from the remaining five address lines, which activate one of the 32 columns. Thus the contents of four memory cells are transmitted to the output amplifier (V). The output can be controlled by the control signals S1 and S2.

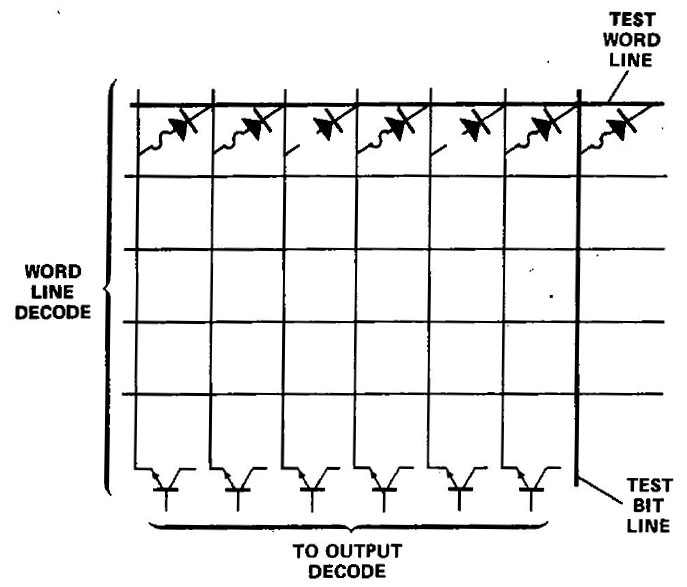

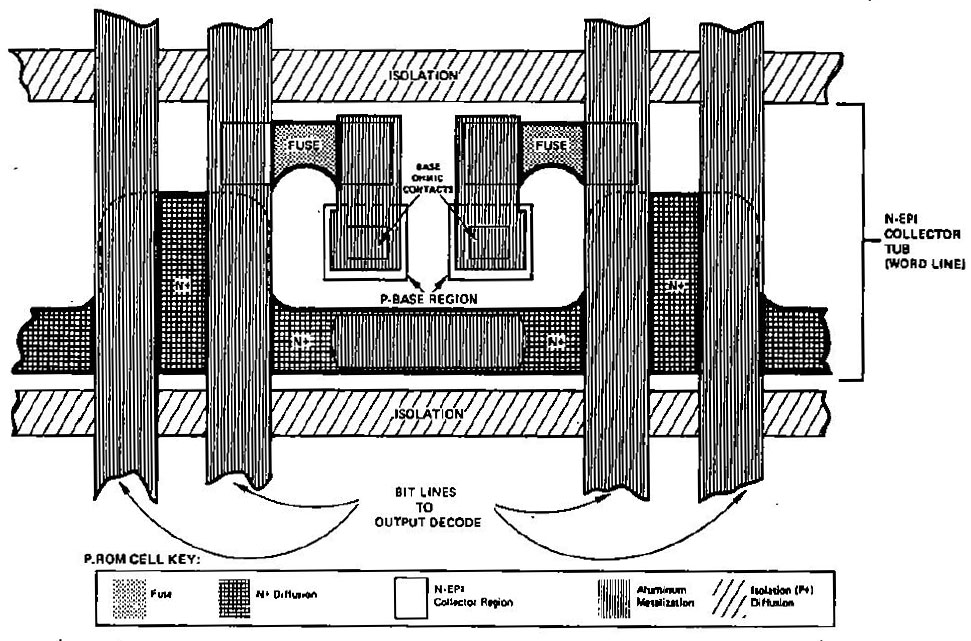

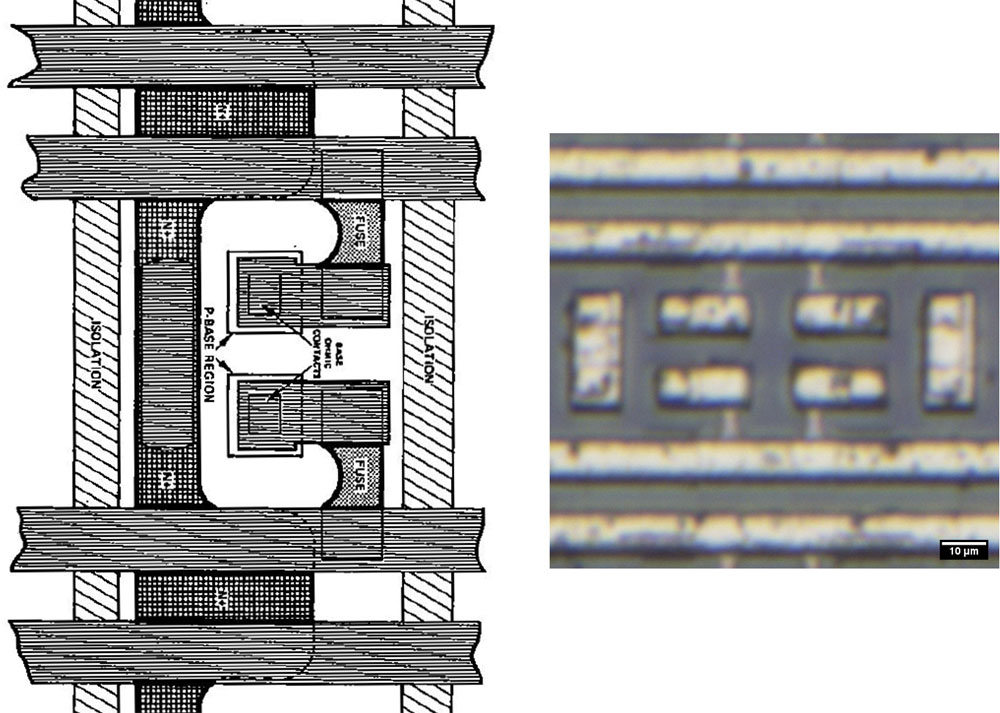

The IEEE paper "A Reliability Assessment of Bipolar PROMs" shows how the memory cells of a bipolar PROM are basically constructed. At the nodes of rows and columns there are fuse elements which are triggered by a current surge during programming. If a row is set to low potential in the circuit shown here, it depends on the state of the fuse element whether the low potential is transferred to the transistor of the respective column. The transistor, which can be activated via its base potential, transfers the state of the active memory cell to the output. The diodes ensure that really only the desired cell is read out and that no unwanted current flows through other areas.

PROMs usually contain a test line and a test column. This is necessary because the functions of a PROM cannot be tested easily after production. If just an unprogrammed matrix exists, it is not even possible to test the selection and sensing circuit. For this reason, a test line and test column are usually integrated, which make it possible to test both writing and reading without influencing the usable area of the memory.

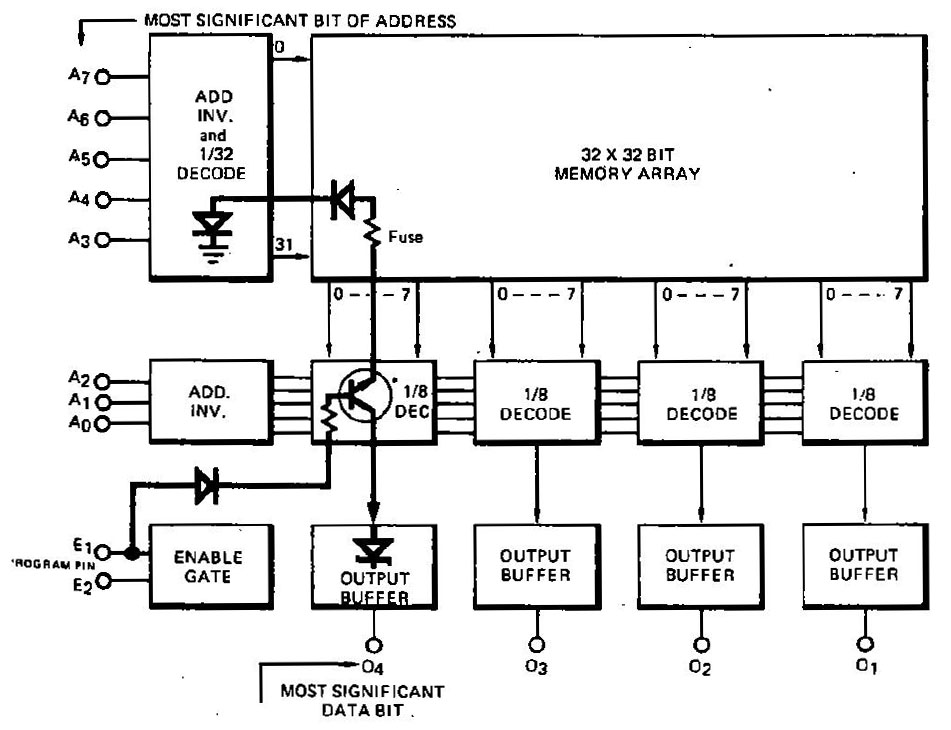

The IEEE article above also provides an overview of the entire circuit of a PROM. The basic design of the PROM shown there is very similar to the MH74S287. However, the MH74S287 works with an inverse logic. Here the address decoder puts one row to ground. The column decoder selects one column each from four groups of 8. When the output is activated, the active transistors pass on the stored information.

Programming is done here by applying a high potential to an enable pin, which triggers the associated fuse element via the transistor in the column selection and the configuration of the row decoder.

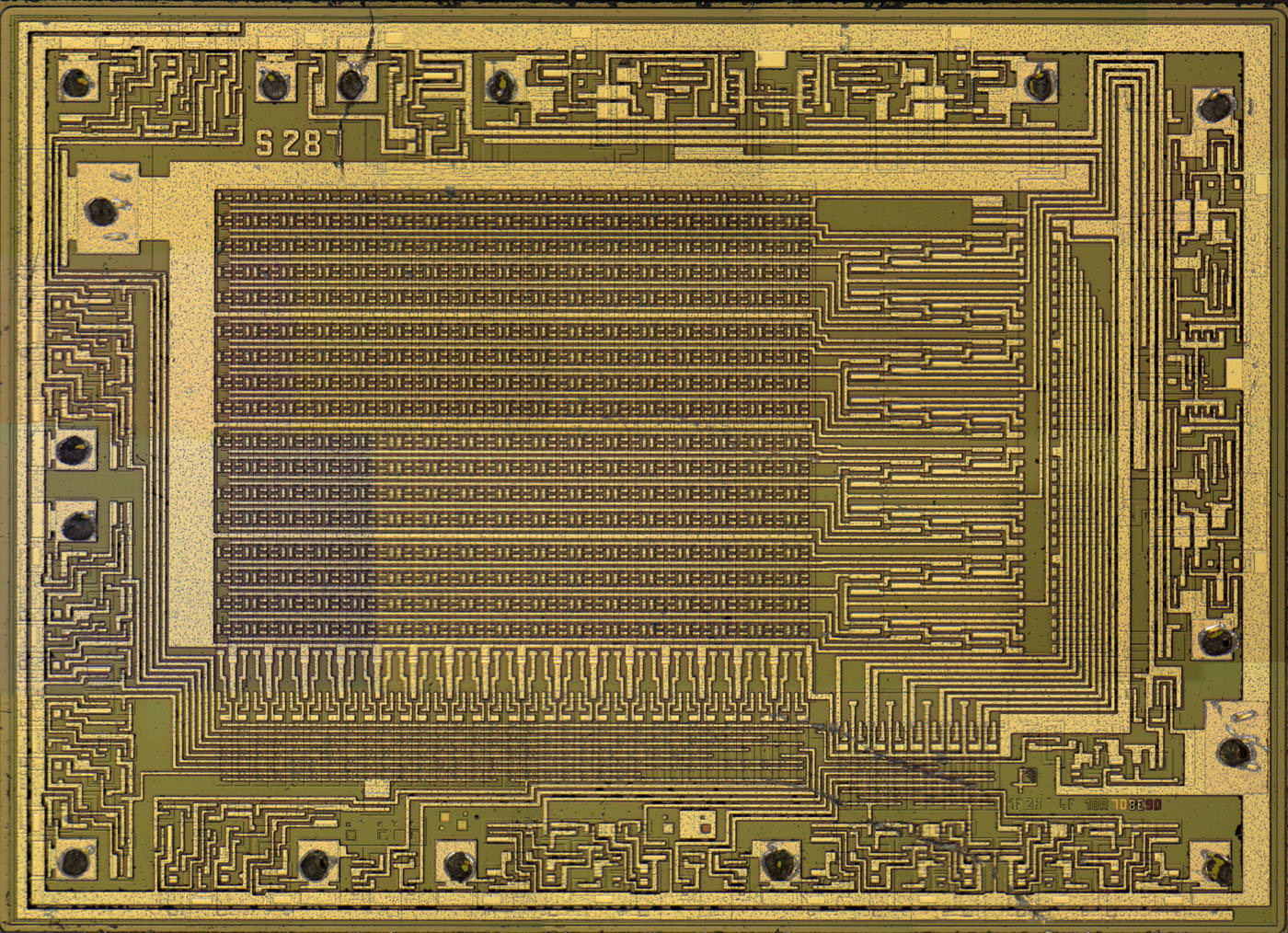

The die of the MH74S287 is 3,6mm x 2,6mm.

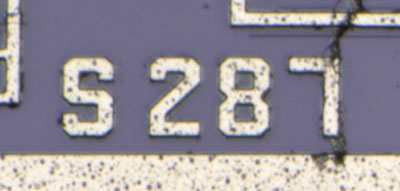

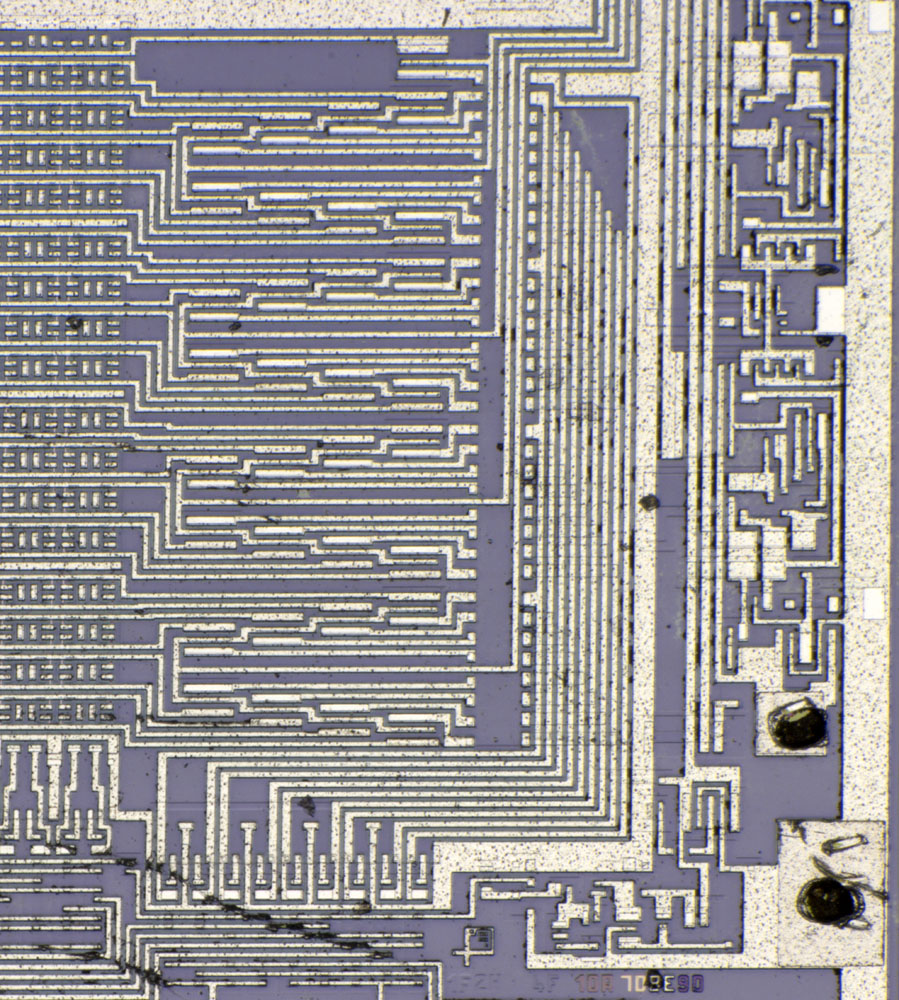

The type designation S287 is shown in the upper left corner of the die.

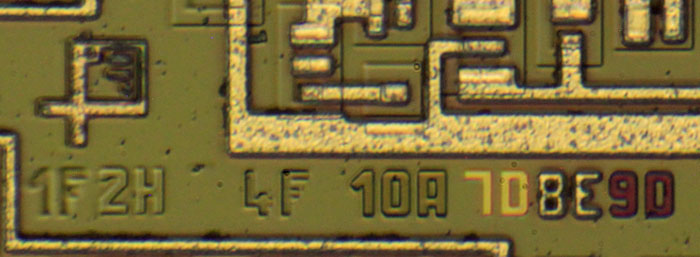

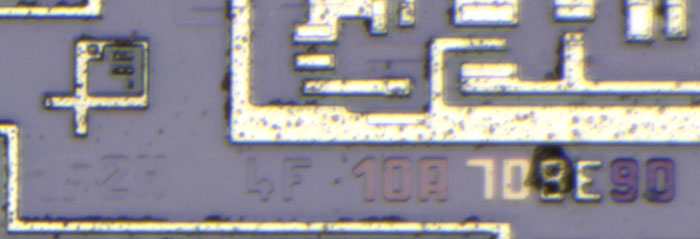

Tesla's logo is shown in the lower right corner. There are also the revisions of seven masks, some of which have been revised very often.

A little further to the left, squares are integrated that allow you to check the alignment of the masks against each other.

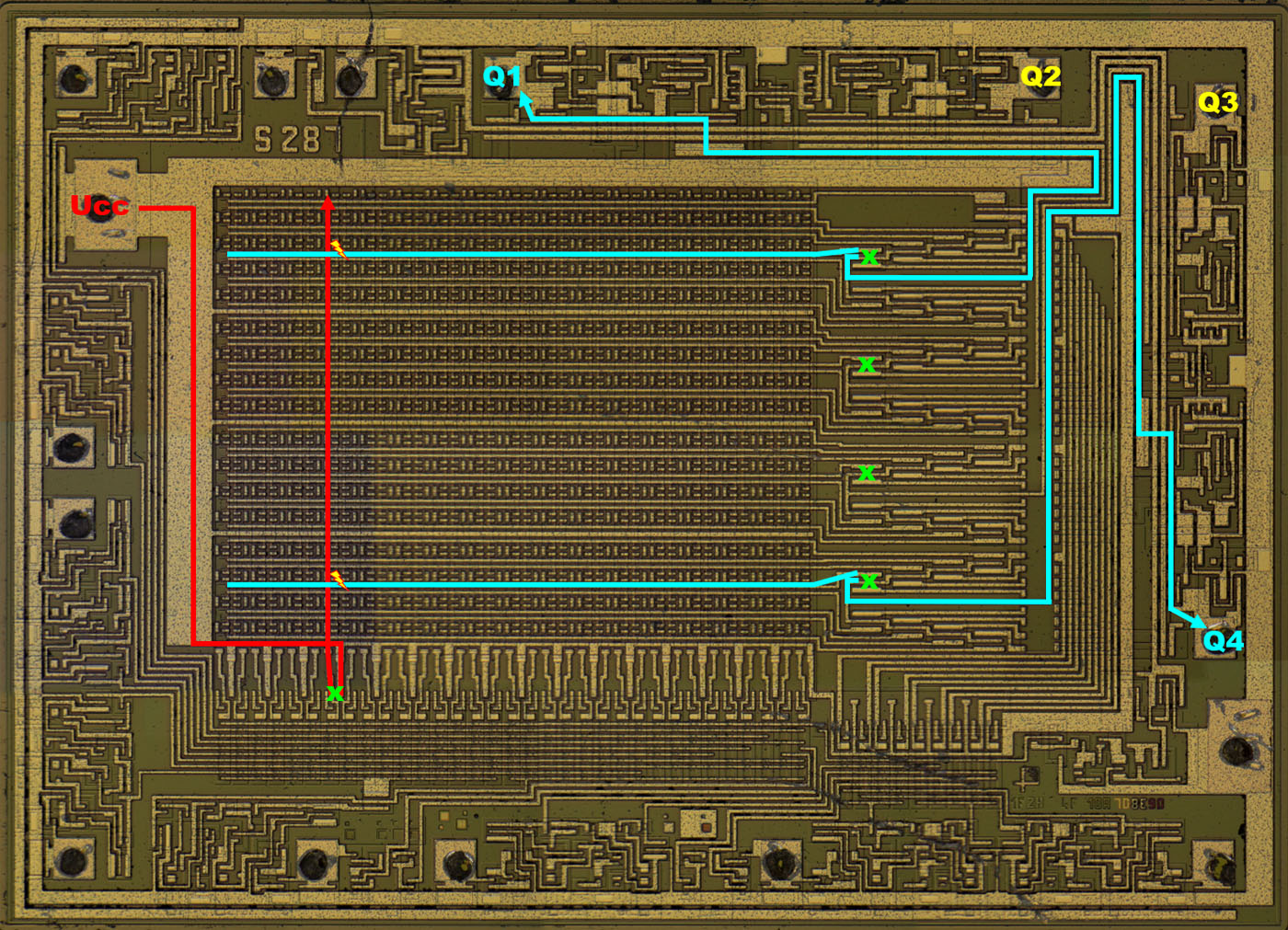

The individual circuit parts are clearly visible on the die. In the center is the 32x32 memory (red), which has an additional test line at the upper edge and an additional test column at the right edge.

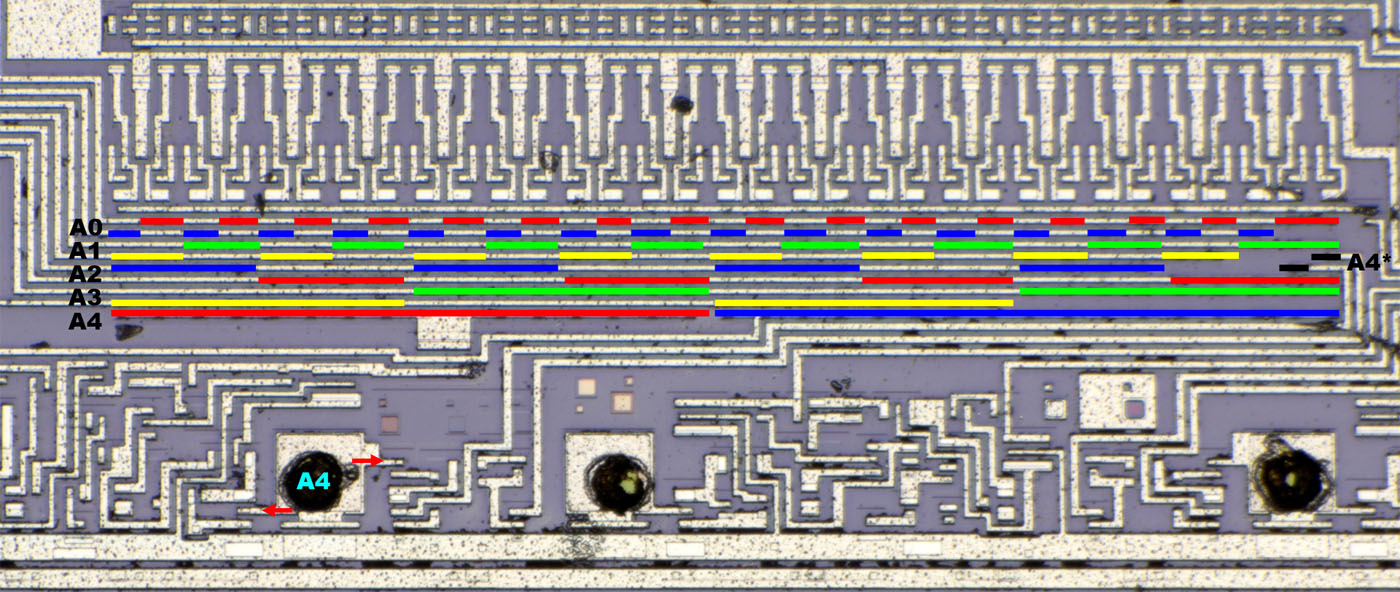

The address lines A4 to A8 are evaluated in the left area (cyan) and fed to the column decoder (yellow) including their complementary values. The column decoder then switches Ucc to one of the 33 columns.

To select one of the 32 columns you already need all five address inputs. To be able to select the test column nevertheless, the address input A4 has been extended with the additional circuit A4*. This is usually a circuit which becomes active only at a voltage which is not present in normal operation. If you want to test the PROM, you apply a slightly higher potential to pin A4 and thus reach the test column.

To the signals of the address lines A1 to A3 the complementary potentials are generated too (dark green) and fed to the line decoder (orange). Here the input A2 offers the additional function to activate the test line. The eight control lines of the line decoder are fed to four blocks, where they select and forward one line in each block out of eight lines (pink). The ninth control line connects the test line to output Q1.

The four tristate outputs (green) are arranged in pairs and share a small circuit section. In the upper left area is the enable circuit that activates the outputs (purple).

The memory area is connected to the Vcc potential with very low impedance. Each of the four blocks is flanked by horizontal Vcc lines.

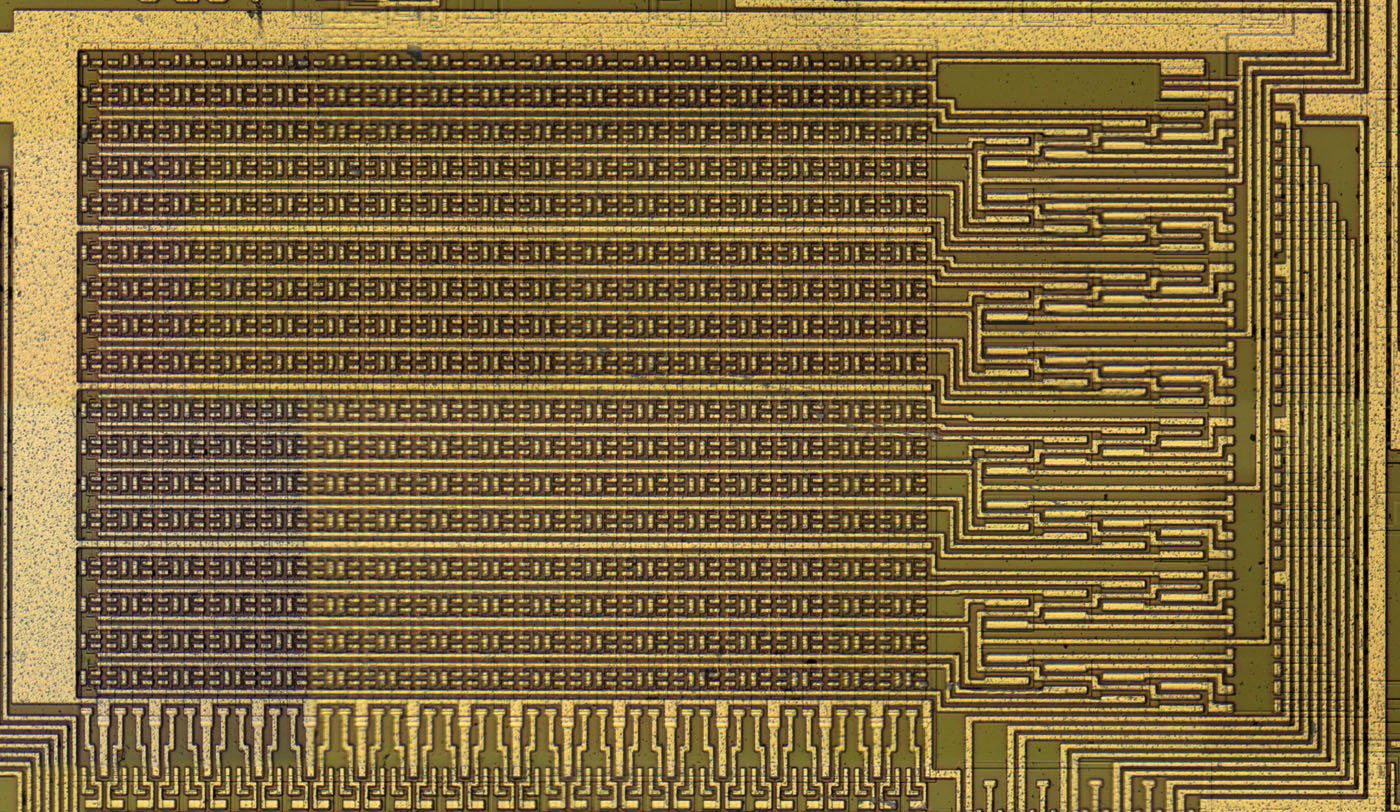

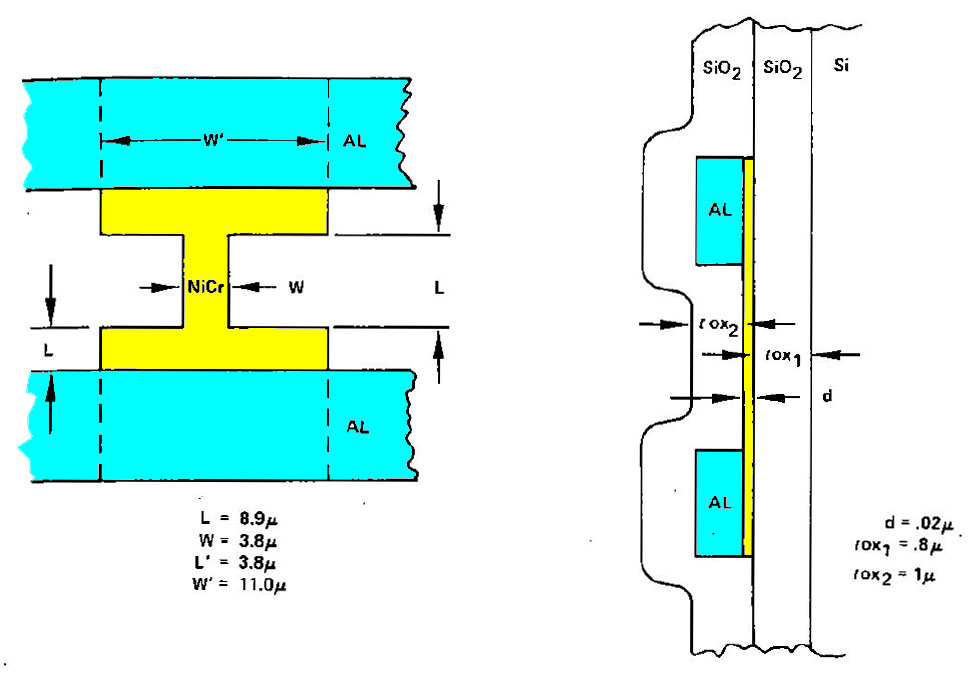

The IEEE article "A Reliability Assessment of Bipolar PROMs" contains a sketch with the typical structure of a bipolar PROM. In this case, the cells are arranged in pairs. The core of the memory cells are the fuse elements, which are usually made of a nickel-chromium alloy. Alternatively, a titanium-tungsten alloy or polysilicon directly has been used. In addition to process-safe manufacturability, low resistance in the intact state and reliably high resistance after the fuse element burns out are important.

In circuit diagrams, base-emitter paths of transistors are often located in series with the fuse elements. Here, there is no emitter. Instead, the base-collector junction has been used as a diode. Below the fuse elements are p-doped squares in the n-doped collector layer. The IEEE article emphasizes the robustness of this implementation. Compared to base-collector diodes, base-emitter junctions are more prone to production defects and failures.

Vertically (horizontally in the MH74S287), the bit lines run in the metal layer. Horizontally (in the MH74S287 vertical) the word lines run, built up with heavily n-doped regions. Between the bit lines, elements of the metal layer reduce the resistance of the word lines. A low-resistance design of these areas but also of the surrounding circuit is important so that a sufficiently high current can flow when the fuse elements are triggered. At the same time, the circuit must also withstand the increased voltage used during programming.

The IEEE article "Reliability Assessment of a Semiconductor Memory by Design Analysis" shows the typical structure of a nickel-chromium fuse. The taper there is 3,8µm wide. This corresponds to the sizes in MH74S287.

Fuses of the metal layer, which are used to adjust integrated circuits, have openings in the passivation layer so that it does not suffer large-scale, undefined damage when the fuse is triggered. This can be seen well, for example, on the die of the LTFLU (

https://www.richis-lab.de/REF04.htm#fuse). The fuse elements of a PROM, on the other hand, are located under the passivation layer. This is possible because they are triggered with much less energy.

The amount of energy and the exposure time with which the fuse elements are triggered are critical design parameters. Strips that are not optimally fused can regenerate. The IEEE article explains this effect in more detail. If the fuse does not fuse far enough, a very high electric field is established in the opening. The metal oxides that have formed there can then cause a breakdown despite the low voltage and for the evaluation circuit the fuse appears intact again.

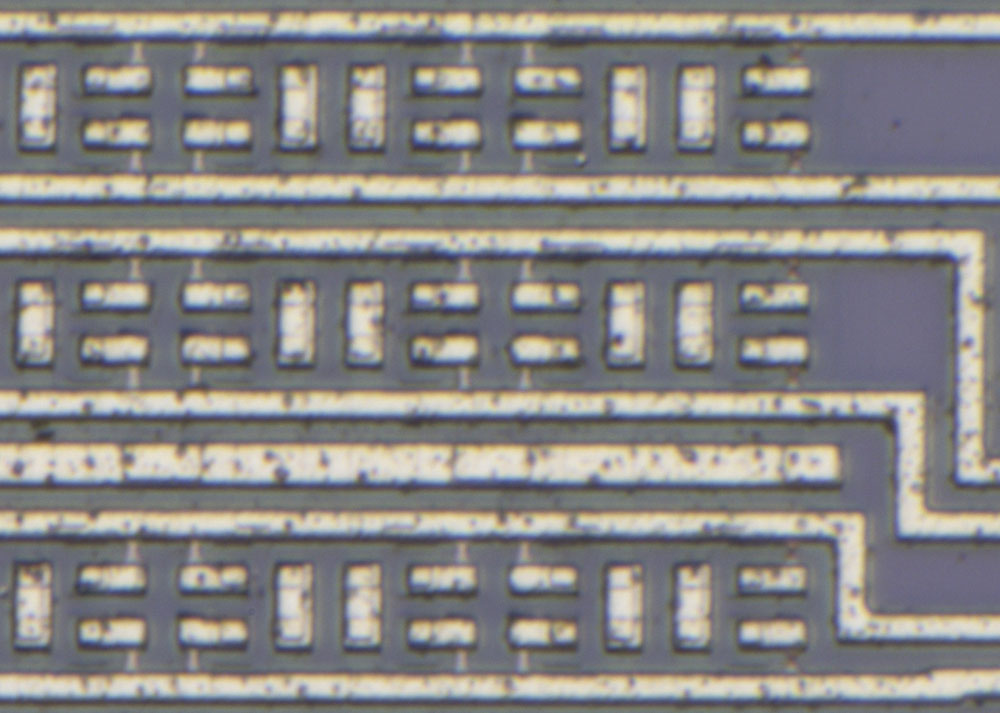

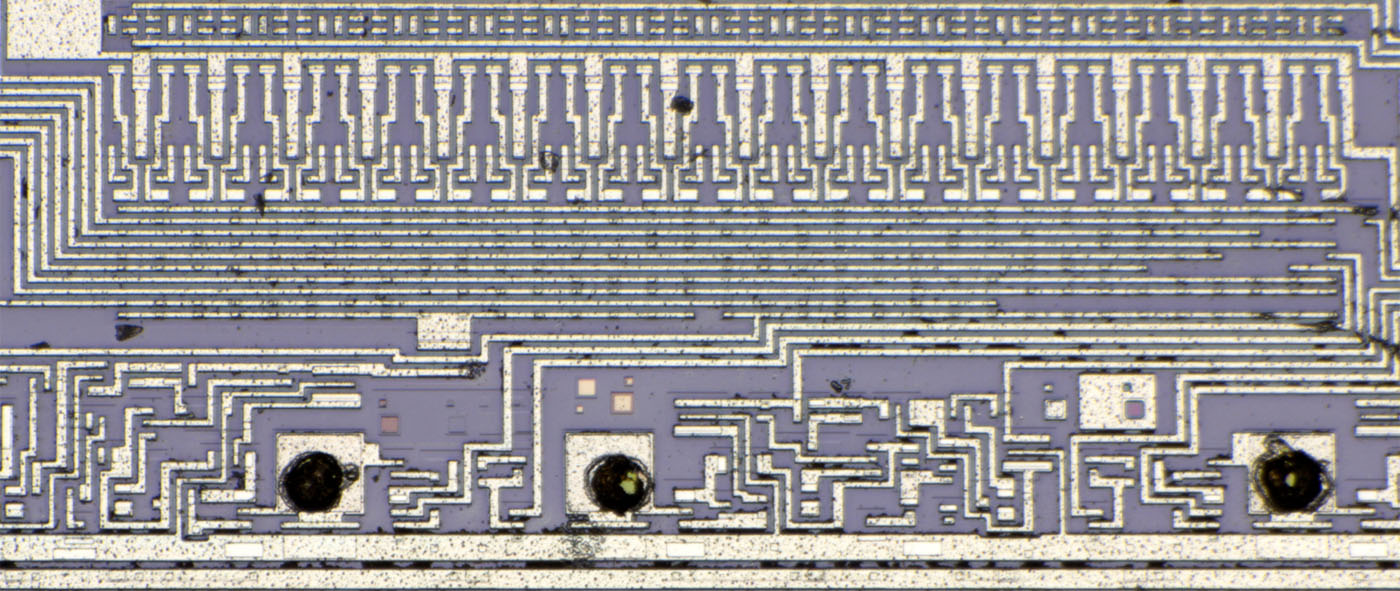

If you compare the sketch from the IEEE article with the memory cells of the MH74S287, you can see that Tesla has always grouped four memory cells together. Otherwise, the structure is apparently the same.

The present device is unprogrammed. You can see the bright fuse elements quite well.

In the test column (far right) you can see how triggered fuse elements look like. The break forms a dark area in the center of the element.

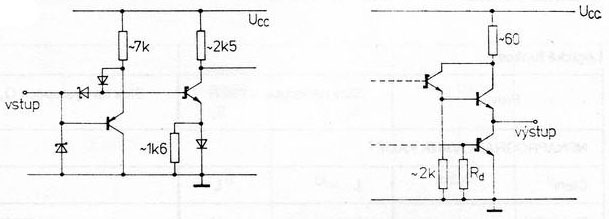

The datasheet shows the input and output circuitry of the MH74S287. Fast Schottky transistors are used there.

The structure of the column decoder can be seen clearly. The interconnection with the address lines and their complementary lines ensures that each address activates exactly one column. The test column on the far right and the column next to it additionally receive the signals A4*, which are generated in the additional circuit of the address input A4. If the 32nd column is selected and input A4 is in overdrive, the additional circuit ensures that the 32rd column is deactiviated and the 33rd column is activated.

To the right of the column selection is the decoder of the row selection (seen here at the lower edge). This works according to the same pattern and outputs nine control signals.

Eight of the nine control signals pass under the continuing lines at each of the four memory blocks. Each memory block has eight larger transistors, one of which is active. A bus line then leads up from each block and to the four output drivers.

If address input A2 is in overdrive, the control signal in the top block jumps to the single transistor at the top edge and the test line is connected to output driver Q1.

Between the line decoder and the GND bondpad there is a small circuit connected to the two decoders. Presumably a bias generator or something like that.

There is a programming instruction for the MH74S287. According to this, the module must first be supplied with its normal operating voltage. Then you set the address you want to write and apply the pattern to be programmed to the outputs. The outputs are either held at high potential by pull-up resistors or pulled hard to ground.

The programming process is done with an increased voltage of 10V to 11V and is controlled by one of the enable inputs. Before raising the supply voltage, disable the outputs. If the correct voltage is applied, one activates the outputs for 1ms. Where a high current flows, the fuse elements are triggered. The high power dissipation that occurs during this process makes it necessary to define cooling times that depend on how long the increased voltage is applied to the device ("Y").

On the die one has tried to make the way the high programming current has to flow as short and low impedance as possible. Ucc is fed directly to the transistors for the column selection. Depending on the state of the address lines, one of the columns becomes active and is supplied with Ucc. On the right side of the memory matrix, one of the rows is switched through in each of the four blocks. Depending on which outputs have a GND potential applied to them, a high current flows across them and the associated fuse elements are triggered.

It is interesting that the output amplifiers seem to be bypassed during programming. From the line selected, a line leads directly to the bondpad via a larger structure. This also explains why a low at the output can be used to disconnect the fuse, but in normal operation a high is present at the output when the fuse is disconnected.

https://www.richis-lab.de/ROM04.htm