Howard,

Can we see what the CP pin looks like with the Rigol loop filter values / old firmware combo?

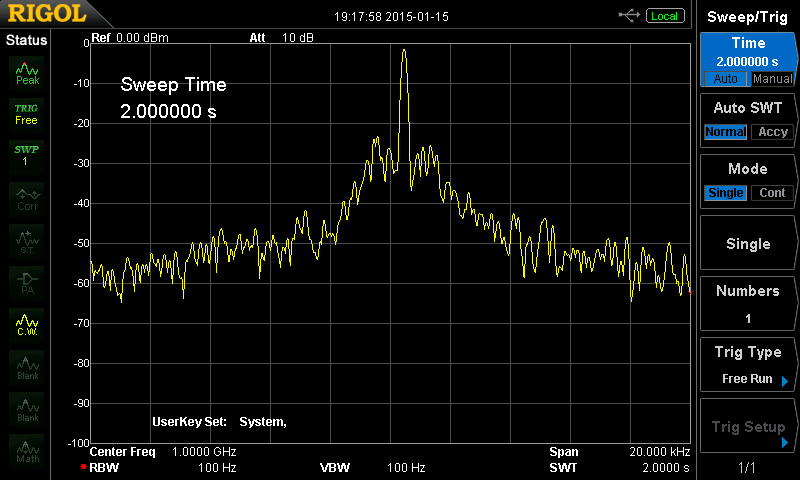

Although unlocked, your eval doesn't have the serious FM happening that we've seen on some of the old firmware and beta units. With the first sideband at -36dB, I'm getting a deviation of 3.1kHz, which translates to a displayed jitter of 20ps pk-pk @5us delay.

The first DS1054Z I looked at had a 50mVpp 100kHz sawtooth happening on the CP pin with the old firmware. You obviously have the 100kHz modulation; I'm just wondering if examining the CP behavior will provide any clues. (But your deviation may be too small to see on CP or Vtune).

Hello Mark.

Sorry, managed to blow up the 4360-7 on the board today when fitting a 25MHz canned oscillator instead of using the sig gen to see if it made any difference. Anyway, I've replaced it now, but debugging that delayed me a while.

The difference between the canned 25MHz reference oscillator and the signal generator in terms of phase noise was negligible as far as I could see, so the measurements I'm showing here are with the HP signal generator (8656B).

Not sure how you want me to measure this, on the scope the CP pin is in the noise at 10mV/div with both old and new register settings. Certainly not 100kHz 50mVpp.

Also, I need to make a correction, the PLL is showing locked on the old values too, it just wasn't being output on the pin due to the registry settings. Doh! Anyway, I guess that's as much to do with the way that the lock is configured and interpreted as much as anything else.

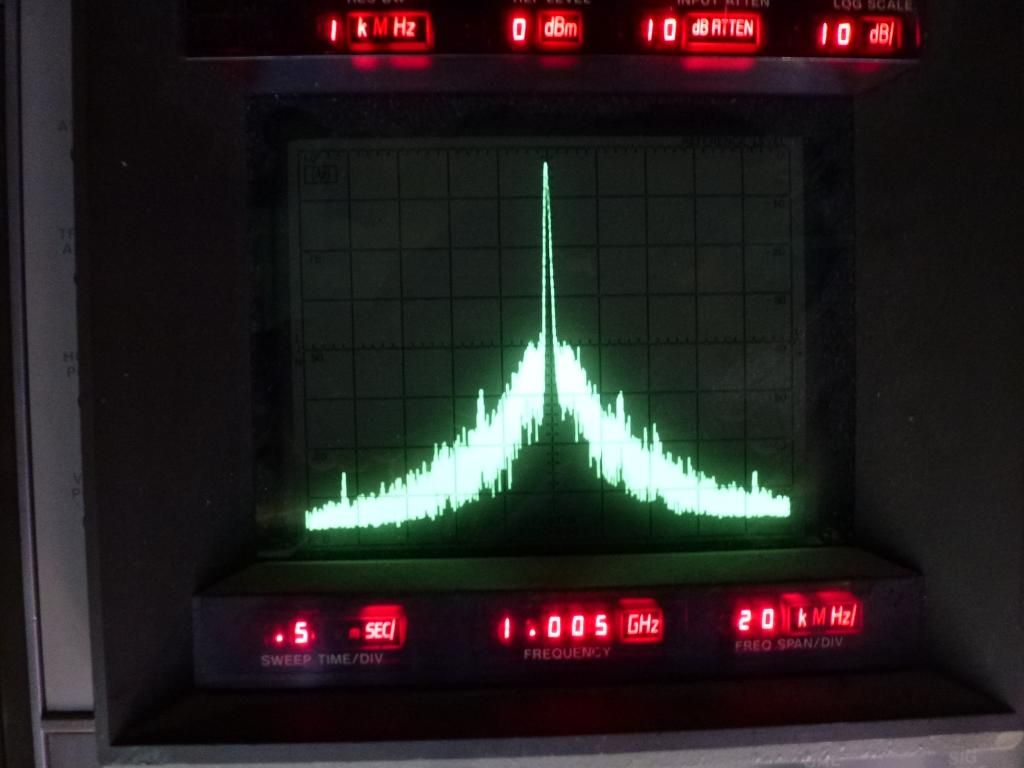

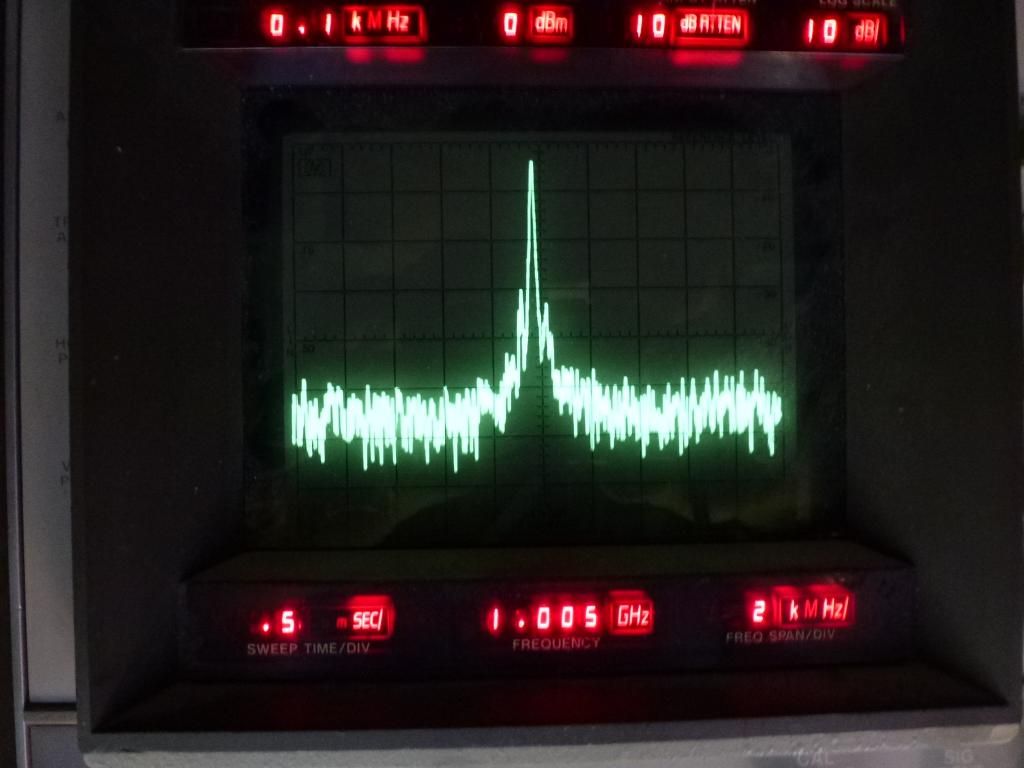

Signal generator phase noise (HP 8656B)

Canned oscillator phase noise (for information, not used in further testing).

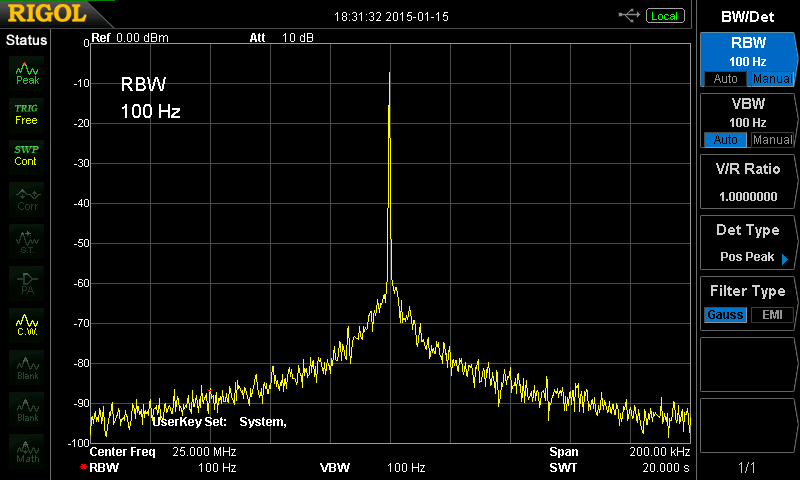

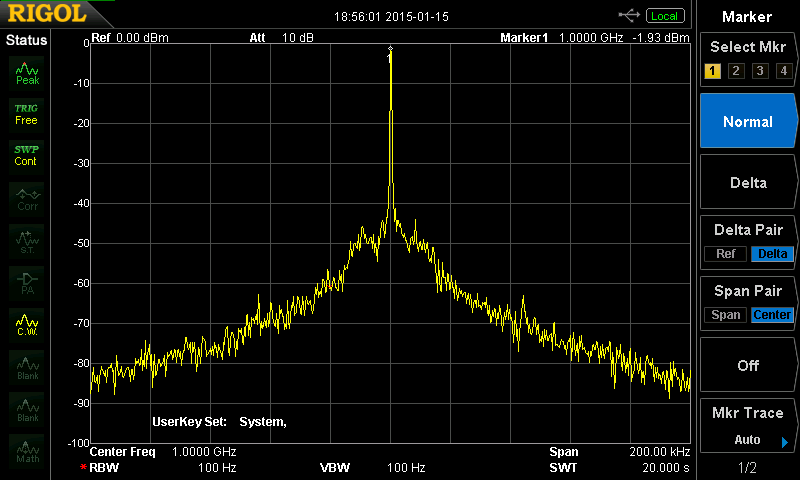

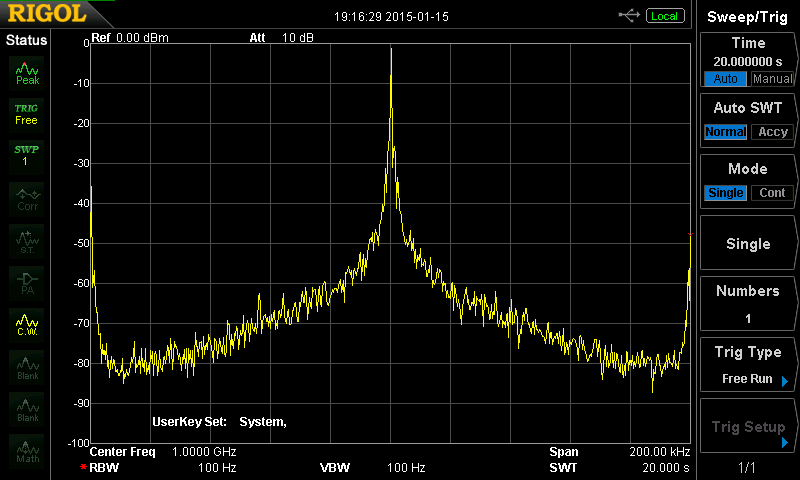

4360-7 output, new firmware 200kHz span

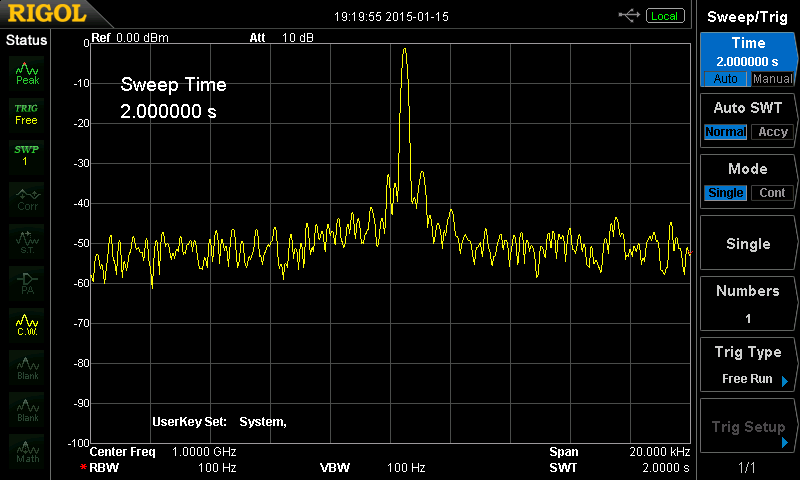

4360-7 output, new firmware, 20kHz span

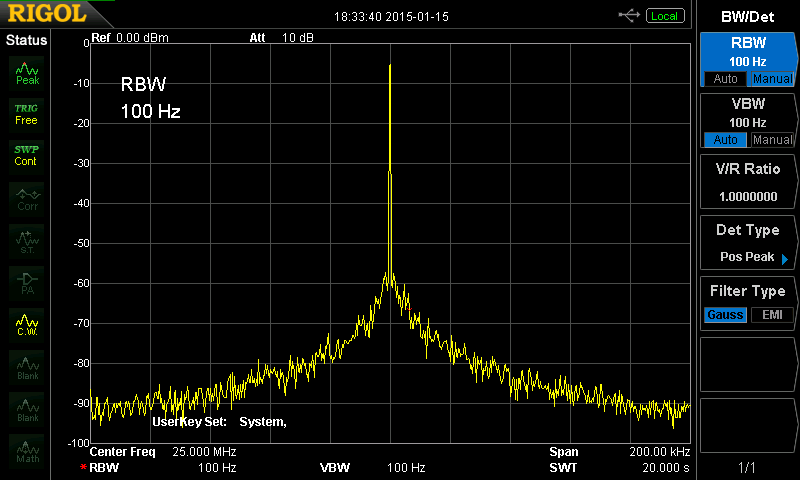

4360-7 output, old firmware, 200kHz span

4360-7 output, old firmware, 20kHz span