A new DS1054Z owner and myself finally got our schedules synced to do some internal measurements on the new firmware, 04.02.SP4.

His particular scope had the 5us jitter pretty bad, about 10ns pk-pk. After the upgrade, as with everyone else, it was reduced to beyond visible in the time domain.

Before:

After:

After upgrade, a long point FFT against a 100MHz signal showed the same characteristic peaking as everyone else has seen around the main carrier at approx 71kHz and 120kHz (this was a 24MPt sample):

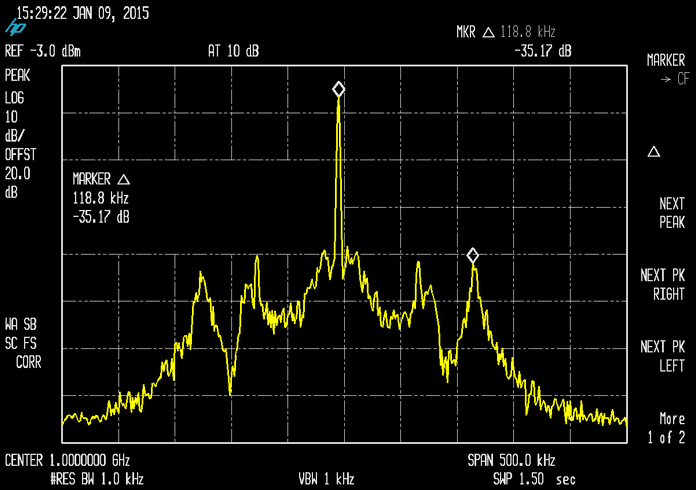

A spectrum analyzer shot of the ADC clock before:

And after:

A plot of min/max hold shows there's quite an amplitude spread, indicating randomness in the clock:

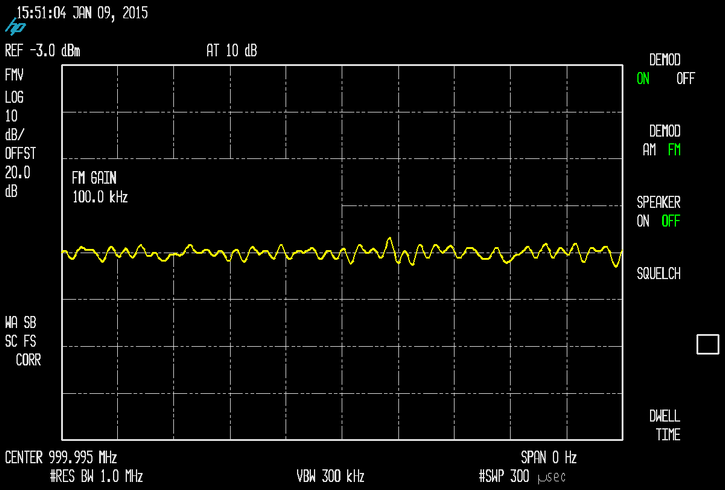

An FM demod of the clock shows no periodicity that I could find, so I don't think it's from a power supply or other external influence. We will take a look at power pins directly for 71kHz/120kHz ripple, but we ran out of time today.

The SPI bus was probed. For comparison, here are the bytes from the beta for the AD4360-7 PLL registers:

02 00 29

40 31 2C

00 19 02

Here are the new values:

22 00 29

40 31 28

00 19 02

I decoded the MUXOUT setting and Rigol left it set to "Digital Lock Detect (Active High)". The MUXOUT pin was probed and except for a brief high pulse of 1.6us on boot when the PLL is programmed, it is at a constant low. There was no further activity on the SPI bus beyond the initial register programming (total of 9 bytes in 3 transactions).

The PLL "Band Select Clock Divider" (x1 --> x4) and "Core Power Level" (20mA --> 15mA) have been altered from the beta to the new release.

So, there ya go. PLL is still definitely not locked, but not wildly flapping either. I don't think we have any examples of it being completely unstable with the new firmware.

We'll try some heating/cooling of the PLL area before we close it back up.