ZX Spectrums have minimalist I/O address decoding. The original rubber key 16K/48K and the ZX Spectrum+ models had no address decoding whatsoever and simply used Z80 address line A0 as the ULA chip select. Later models kept the A0 ULA /CS for compatibility and added partial address decoding for their new hardware functions using A1 as /CS. This means that many I/O addresses are forbidden and will cause contention if used for external peripherals. As 'short' Z80 I/O addresses are only 8 bit, if you have extra devices like Interface 1 on a rubber key speccy, there are only five low byte address lines left, which vastly complicates interfacing peripherals that need several address lines + a decoded /CS. If you need your hardware to be safe plugged into any speccy, you must avoid any address with A4, A3, A1 or A0 low.

Completely agree. Initially I will make sure this 'bread boarding design' (not my interface) is working okay with a 74LS138 and just use an existing port like $1F (Kempston 1) to test that everything is working okay. I will then exchange this for a CPLD and use all 16 address bits & required control signals. As I am new to CPLD, apart from a few fundamental experiments, I wanted to get my design proved working with partial decoding first, one step at a time.

LEDs on the un-decoded address, and data and control bus are essentially worthless on any Z80 system where you cant stop the clock (e.g. a ZX speccy, because it uses DRAM refreshed by the Z80, so stopping it crashes the system within a few ms) as the refresh cycle will cause activity on A14:A0 . OTOH if you use transparent latches to drive the LEDs, and decode a suitable gate signal for the latches, you can get a useful indication.

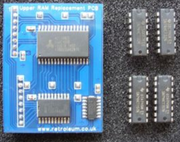

Yes I did wonder about the refresh cycle so I was going to replace my DRAMs with SRAMs like these replacement modules ...

Actually as I type this I just got a notification of a update to this post and read that Tom actually recommends SRAM too. Hopefully this is correct then.

As the ULA provides the clock for the Z80 on the Speccy, I was unsure if I would be able to slow down the speccy enough, without it effecting 'other stuff', to make looking at the signals via LEDs waste of time or not.

There are 2 additional reasons I thought about using LEDs;

1) So that I can use this same design on other boards like my RC2014 etc that do have the ability to single step

2) Fault finding a dodgy Speccy for stuck bits on faulty DRAMs.

OTOHMaybe a better approach is to forget about the above and to narrow my focus and make this breadboard design just for the Speccy and my current project using port I/O. With that in mind, it may be a better idea to forget about the Address & Data LEDs and just use LEDs on the control bus as this will at least give me useful information I can see with the speccy running at full speed.

If your breadboard device is 'write only' i.e. never responds on the data bus and doesn't assert any Z80 control lines, you can put all decoding after a unidirectional output only buffer.

However if you need to read bytes from your breadboard device, you *MUST* have enough address decoding in front of the buffer's output enable to avoid contention when the direction control selects it for input. If on a ZX Speccy any of the address lines I mentioned earlier are low, the buffer *MUST* be disabled.

Thank you, I understand what you mean a little better so I will need decoding first.

Summing UpNarrow my focus to this project only. I guess my main priority is wanting to keep my Speccy alive while still learning. After that I would like some indication, via LEDs of what is going on with my circuit.

With this in mind maybe a better approach is to;

1) Just use current limiting resistors on the lines for protection against myself and forget buffers altogether.

2) Decode the address lines after the limiting resistors. Initially with a 74LS138 then later CPLD.

3) Check correct design for RD/WR IORQ M1 etc with address lines to activate the decoder.

4) Use a driver for the control signal LEDs. Maybe ULN darlington type. Will investigate.

Better?

Thanks again, really appreciate