I thought I'd finish my trip down memory lane with a look at interfacing dynamic RAM.

The systems that I built with large (i.e. > 64k) RAM had a DRAM interface for 2 banks of 256k x 1-bit DRAMs for up to 512k bytes of memory though I ended up with two systems which had 256k as I could only afford 16 DRAMs.

I confess here that this is not my original circuit - it's a fresh design based on a couple of things that I remember about the original - mostly that I only used a couple of flip-flops and I'm sure that I implemented CAS before RAS refresh to get around the fact that the Z80 only has a 7 bit refresh counter. It "feels about right" though

This does mean I can't guarantee that it would work if implemented. I don't view that as too much of a big deal though since I don't think I'd bother these days. At the time 8k x 8 was a huge SRAM so to get 512k would have taken 64 chips - just not practical and much more price-wise than 16 DRAMs. Since you can now get much larger SRAMs I don't think I would bother with the complexity for a small Z80 SBC

That said it's not all that complicated, what complexity there is comes from the fact that DRAMs have a multiplexed address bus and need to be periodically refreshed, fortunately the Z80 does some of the work for us by providing a refresh signal and a row counter for refresh addresses. Unfortunately anything bigger than a 16k DRAM tends to have more row address bits than the Z80 provides.

There is an excellent document produced by Mostek regarding dynamic memory which you can read

herePretty much all the designs I've come across are based on the 74LS157 quad 2-input multiplexor.

The first thing to look at is the timing diagram - the Z80 has two memory read patterns and one memory write. Of these the opcode fetch or M1 cycle has the tightest timing so most people design to that and the longer memory read/write cycles should then take care of themselves.

Here's the timing (mostly without taking gate delays into account).

One thing to notice is that RAS is just a copy of MREQ (that's handy!). Using RAS before CAS means that the multiplexing signal which drives the 74LS157 just needs to be copy of MREQ which is not active during a refresh cycle - easy to drive with a couple of gates (the slight delay this produces helps to ensure that the row address hold times should be easily met).

That just leaves CAS - this was generated in two halves. The first is a copy of MREQ which is delayed until the start of T2 (CASm on the diagrams). For a 4MHz Z80 MREQ is guaranteed to be not more than 85ns after the falling clock in T1 so that gives us about 40ns of RAS to CAS delay which should be OK.

The second part of the CAS signal is active during refresh - this is generated as a shortened version of the RFSH signal. In this case we start CAS with the falling edge of RFSH but deactivate it with the next rising clock edge. This is CASr on the diagrams.

The two signals are then combined with an AND gate,

Finally RAS is not quite an unmodified MREQ - we will probably want to supply an enable signal from the address decode logic, however we do not want this to interfere with RAS during the refresh cycle so we gate it with a select plus RFSH to generate the actual RAS circuit.

The circuit ends up looking like this.

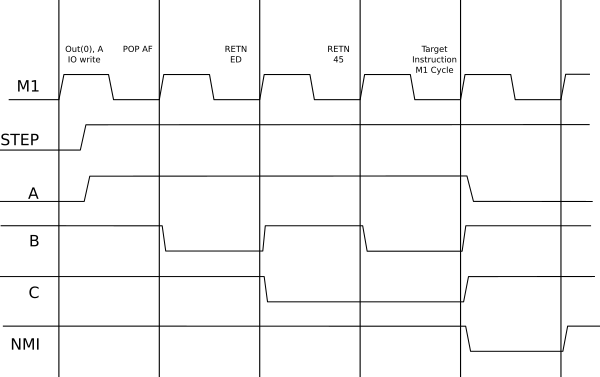

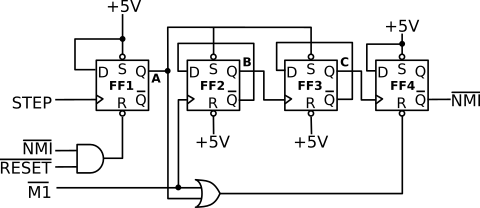

EDIT: Looking at something else I chanced upon the fact that the above circuit is nothing to do with the memory interface - it is the Nascom 2 single step circuit. I obviously overwrote the old image my error. I'll try to restore the correct diagram.

I think it should work with most 64k x 4 DRAM chips. Clock to CAS should be about 40ns with LSTTL, for a 4MHz Z80 there's a 35ns data-in set-up time so the RAM needs a CAS access time of 250-(40+35) or 175ns, give-or-take. As even the venerable 4116-25 had a T

CAC of 165ns I don't foresee any problems with anything faster. For a 6Mhz system the figure will be about 100ns which shoulkd be do-able with a "150ns" DRAM.

The only thing I can see that might be iffy is whether there's enough CAS precharge time for the refresh cycle. One problem is that there is no specification for the interval between MREQ going inactive and RFSH going active - however it's probably 40 or 50ns on a 4MHz part which

should be enough, 6 or 8MHz parts might become marginal here. Wiser heads might spot other mistakes I made.

If anyone does implement it, let me know if it works

Edit: Re-reaading the Mostek document I was reminded of one small tip which had elluded my memory - it's wise to latch any address bits which are used to generate chip select signals with the falling edge of MREQ. The Z80 doesn't guarentee that the address bus will be valid for the whole of the time that MREQ is low. Thus it is possible to get short glitches on chip select signals which can cause problems - especially when used to generate RAS signals for DRAM.